视频控制器是什么

的有关信息介绍如下:

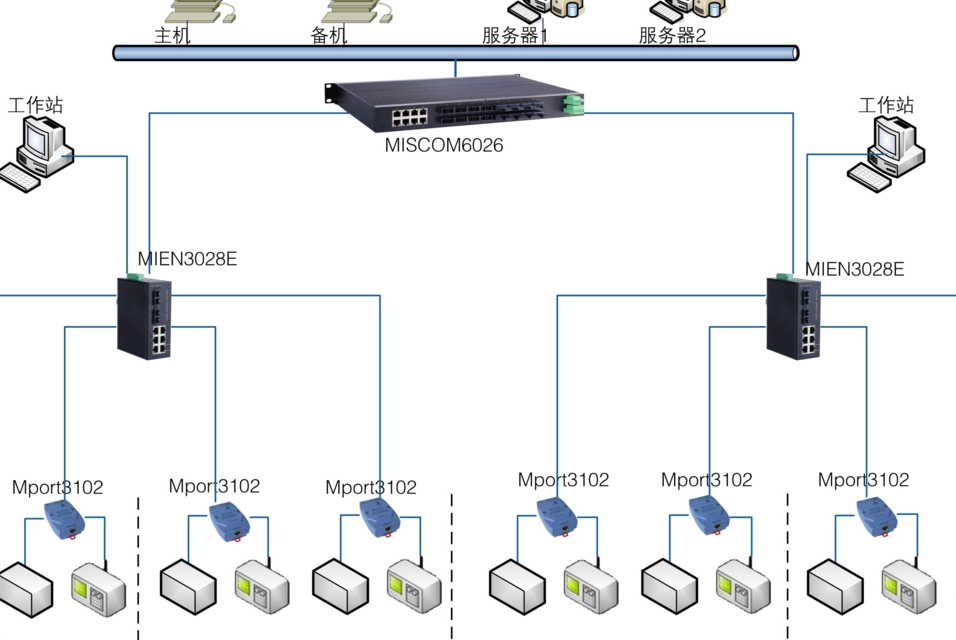

视频控制器一般由显卡驱动程序或DirectX中自带 视频控制器模块是芯片与显示平台的数据接口,对检验芯片设计是否成功起着重要的作用,有必要把它单独划分为一个子模块。为了提高设计的成功率,在设计初期采用了基于FPGA的原型验证。整个系统的FPGA原型验证平台如图1所示,平台分为2个部分,硬件设计和基于RISC CPU的软件解码,两部分协同工作,既可以验证软件和硬件的解码结果,又可以加速整个解码过程。 图1 H.264解码芯片的FPGA原型验证平台 图2 输出视频控制模块结构框图 视频控制模块的设计与实现 视频控制模块原理框图及功能分析 输出视频控制模块的结构框图如图2所示,本模块有2个时钟域:系统时钟域和显示时钟域。系统时钟频率根据所选用的SDRAM类型而采用固定的166MHz;对于分辨率为1280×720的高清电视来说,显示时钟域可以选用70 MHz 左右的频率。 系统时钟域含有2个对外接口:系统接口,主要包含上层系统发出的指令以及输出控制模块的反馈信息;DRAM接口,包含数据专用总线为输出控制模块提供的信号,用来于向DRAM请求显示的图像数据。 系统时钟域中的显示输入控制子模块(Disp In Ctrl)首先用于接收系统传来的StartDisp和EndDisp信号,来启动或关闭视频数据的输出显示功能,同时发出帧图像显示完毕信号(FrameDone),通知系统更换下一副图像的地址信息(ImageAddress);其次,它用于向DRAM发出请求,通过专用数据通道读取需要显示的图像数据;它还要控制输入多路选择模块(Input MUX),从而完成向片内SRAM写数据的任务;最后,该模块要与显示时钟域的信息交互,向时钟域同步模块(Clk Domain Sync)发送显示使能信号(DispEn Sys),控制图像显示的开启和关闭。系统时钟域的另一个子模块——输入多路选择模块会按照一定的规律选择片内双口SRAM,控制存储器地址,完成向存储器写入显示图像数据的任务。 显示时钟域含有一个对外显示设备接口,主要包含用于显示的控制信号和已完成转换的数据信息。显示时钟域包含2个子模块,一个是输出多路选择子模块(Output MUX),用于实现对双口SRAM的选择和地址控制,按照一定的规律读取要显示的图像数据;还要进行数据的打包。另外一个子模块是显示输出控制模块(Disp Out Ctrl),用于实现对TV编码器的控制、YUV信号向RGB信号的转换以及对数字图像的缩放,信号包括显示时钟、行同步、帧同步以及RGB图像数据等;它还要控制输出多路选择模块以读取显示数据;最后,它要与系统时钟域进行交互, 配合数据在两个时钟域之间的传递。 视频控制模块采用的特殊技术 时钟域同步模块是输出控制模块设计的重点,它主要负责两个时钟域之间的控制信号传递。跨时钟域的信号传递设计较为麻烦, 所以设计中将传递的信号分为两类:数据信号和控制信号,其中控制信号就是通过时钟域同步模块传递。对需要跨时钟域传递的信号数进行精简,在最后方案中只需要2个信号:WrDone信号由系统时钟域发出,通知显示时钟域某块双口SRAM中的数据已经更新完毕,可以读取并进行显示输出;RdDone信号由显示时钟域发出,通知系统时钟域某块双口SRAM中的数据已经显示完毕,可以更新其内部的数据。信号在不同的时钟域之间传递需要采取消除亚稳态(Metastability)的处理措施,可使信号通过两级寄存器锁存输出,如图3所示。 图3 跨时钟域信号亚稳态消除电路 图4 视频输出子模块的硬件实现框图 设计中有两点值得注意,首先,时钟域同步电路应放在一个独立的模块中,保证综合工具的优化、时序分析的正确,并方便电路的分析和调试;同时,为了能够使信号的目标时钟域采集到信号变化,设计中传递的控制信号都采用电平信号表征。 时钟域之间要传递的另一种信号是数据信号,由于数据信号数目较多、变化也较快,所以它们的传递通过双口DPRAM实现。双口DPRAM要求读写端口对同一存储地址的操作要满足一定的时间间隔,否则会出现数据传输错误,甚至会破坏硬件电路。因此为了避免DPRAM的读写冲突,设计中采用了“乒乓”缓冲的方法,两块DPRAM交替存取解码后用于显示的亮度或色差数据:当显示部分读取一块DPRAM中的数据时,系统向另一块DPRAM中写接下来要显示的数据,数据读取完毕时,两块DPRAM就进行交换。这部分共用4块DPRAM来实现,2块传递亮度信号,2块传递色差信号。 下面分析在视频控制器显示输出子模块中运用到的格式转换算法、图像缩放处理算法以及它们的硬件实现。 显示数据格式转换分析 根据Sil 164 DVI信号编码芯片资料,同时参考H.264视频编码标准中给出的YUV → RGB转换格式,故在设计中采用的固定转换算法如下式所示: 上式经过定点化处理,使用移位和相加的方法实现了转换,如下式所示: 在硬件设计中的YUV、RGB信号都是用8位无符号数表示,中间变量采用12位保证精度。最后要在0~255的范围内对计算出的RGB结果进行剪裁处理,式中的幂指数和除法运算都通过移位来实现。 数字图像缩放的算法分析 对于一幅分辨率为M×N的原始图像,其所有采样点的YUV值可以用M×N阶矩阵表示为: 像素点用f(m,n)表示,其中0≤m≤M,0≤n。对一幅数字图像进行缩放,其实质就是对一幅数字图像进行重采样,假定对原始数字图像高和宽进行缩放的缩放倍数分别为S1和S2,那么根据奈奎斯特采样定律,应该用新的水平与垂直采样周期740)this.width=740" > 对原数字图像进行重采样。得到经过缩放的数字图像f′(m′,n′): 由上式可知,经过缩放的数字图像中的每一个重构像素f′(m′,n′)就是原来数字图像各个像素的加权和。若采用该式直接进行硬件设计,计算量会非常大。为了简化设计难度,节省芯片成本,可以在对图像品质影响不大的基础上对上式进行简化。重构后的图像像素值主要取决于两个抽样函数乘积的值。在实际中只采用的值等于1的点,即满足的点。进一步简化,可以取,表示对数按四舍五入取整,得到简化表达式:f′(m′,n′)=f(m,n)。 数字图像格式转换与缩放的硬件实现 设计本项目的时候,显示设备采用分辨率为1280×720的高清晰度电视机,输出到高清晰度电视机显示时采用图像中心对齐的方式。当把解码好的数字图像数据送到高清晰度电视显示时,如果不经过图像缩放处理,那么显示屏幕中间放解码好的数字图像,其他的地方用黑色填充。在进行缩放处理时,遵循上面的规律。先把视频控制器输出模块前端按照逐行扫描排列好送来的数据进行数据格式转换,再把RGB不为零(即不为黑色)的像素数据按每帧和逐行扫描规律轮流放到两块同样大小的片内缓存RAM中,如图4所示。 其工作方式与前面的DPRAM相同,读取RAM1或RAM2中数据的地址后,可以通过地址译码器得到该点像素值的行列地址,即得到m、n的值。把m、n值送到图像缩放处理单元,通过缩放处理得到新的图像数据和新的图像数据地址,再通过写地址译码器得到在输出RAM3中按照逐行扫描格式输出的地址,该地址用来存放格式转换后的数据。最后,从存储转换数据的RAM3中可以直接输出显示所需要的RGB数据。 结语 设计完成后,此视频控制器模块经综合工具Synplify 7.6综合,可以得到80.3MHz的工作频率。与前端的解码模块一起下载到Xilinx公司的Virtex-II 6000型FPGA中,并将其集成入H.264视频解码验证平台上,工作频率可达34MHz,在高清晰度电视上播放图像时效果较好。